ddr ram pinout|Hardware and Layout Design Considerations for DDR Memory : Bacolod 24 rows — Mar 1, 1998 — DDR: Double Data Rate; DIMM: Dual Inline Memory Module; . Call Of Duty's first Xbox Game Pass beta is upon us - with the Black Ops 6 early access beta being included in the subscription this weekend. Alternatively, pre-ordering the game will also grant early beta access, if you're not subscribed to Microsoft's service.

ddr ram pinout,32 rows — Mar 1, 1998 — 184-pin DDR SDRAM DIMM. DIMM: Dual Inline Memory Module; SDRAM: Synchronous Dynamic Random Access Memory, Synchronous to Positive Clock Edge. DDR: Double Data Rate; 184-pin DDR DIMMs use two notches on each side to .ddr ram pinoutDDR: Double Data Rate; DIMM: Dual Inline Memory Module; SDRAM: Synchronous .

185 rows — Hun 28, 2018 — Pinout of DDR SDRAM DIMM (184 pin, Unbuffered) and .DDR (DDR1) was superseded by DDR2 SDRAM, which had modifications for a higher clock frequency and again doubled throughput, but operates on the same principle as DDR. Competing with DDR2 was Rambus XDR DRAM. DDR2 dominated due to cost and support factors. DDR2 was in turn superseded by DDR3 SDRAM, which offered higher performance for increased bus speeds and new features. DDR3 has been superseded by DDR4 SDRAM, which was first produ.

24 rows — Mar 1, 1998 — DDR: Double Data Rate; DIMM: Dual Inline Memory Module; .Pin descriptions and other pinout information can be found in the documentation for Micron DDR3 memory modules. Download. 0.The pinout for the DDR interface facilitates ease of routing to a standard JEDEC DIMM connector. For non-DIMM topologies (that is, discretes), DDR de vices should be .Front and back side of the module, dimensions, numbering of contacts. Pinout of the slot (connector, socket) of DDR4 DIMM RAM on motherboards. DDR4 DIMM - Connector (slot) pinout. VDD is the .Hardware and Layout Design Considerations for DDR Memory DDR3 SDRAM Specification. 204pin Unbuffered SODIMM based on 1Gb E-die. 64-bit Non-ECC. 78/96 FBGA with Lead-Free & Halogen-Free. (RoHS compliant) INFORMATION .Features. DDR3 functionality and operations supported as defined in the component data sheet 240-pin, unbuffered dual in-line memory module (UDIMM) Fast data transfer .Hun 6, 2022 — According to 7 reports in our database (1 positive and 0 negative) the SDRAM DIMM (168 pin, Unbuffered) pinout should be correct. Is this pinoutThe DRAM memory itself, which comprises of everything described above; A DDR PHY; A DDR Controller; Figure 10: DRAM Sub-System There's a lot going on in the picture above, so lets break it down: The DRAM is .As of this writing, DDR II RAM has been standardized. It is the third generation in this series: SDRAM/DDR RAM/DDR II RAM. DDR II RAM will have an effective clock rate of 400 MHz at introduction. DDR RAM is organized in rows or memory pages. The memory pages are divided into four sections, called banks. Each bank has a kind of register .

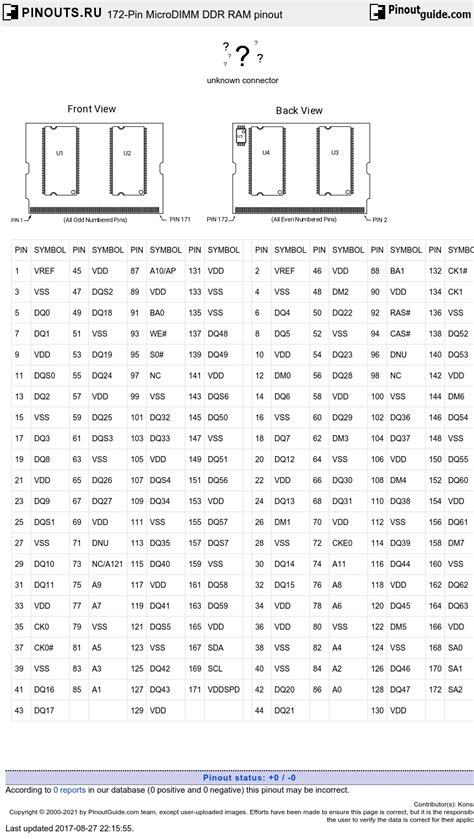

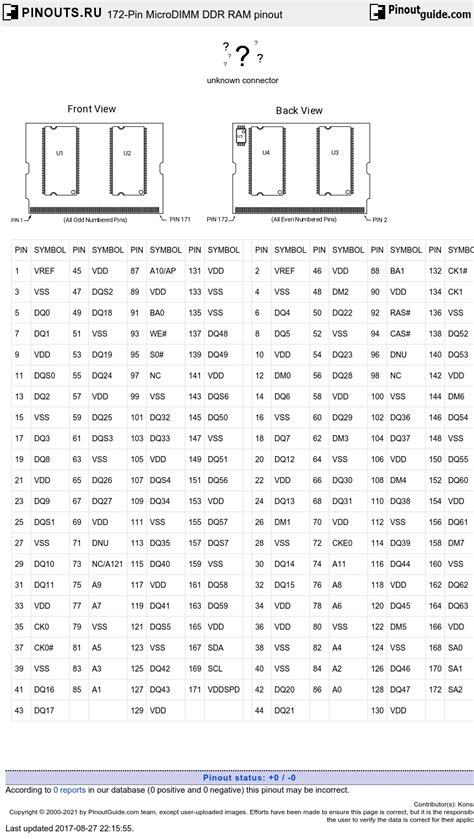

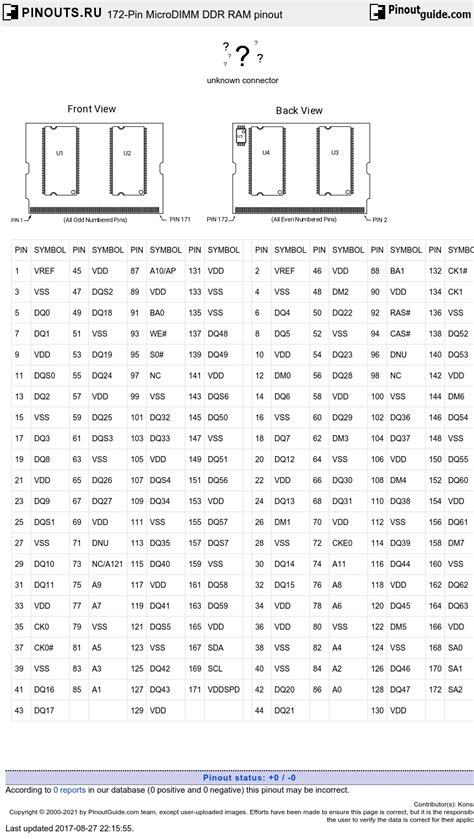

VDD is the memory supply voltage.; VDDSPD is the supply voltage of the microcircuit that stores SPD data.; VREF - reference voltage, usually equal to VDD/2. Usually formed by a resistive divider from the memory supply .

Abr 6, 2022 — 文章浏览阅读1w次,点赞17次,收藏144次。本文深入分析ddr协议,详细介绍了ddr信号的六种类别,以ddr3为例探讨信号作用,如cke、cs#、odt、zq等。同时,文章阐述了ddr颗粒的地址映射关系,解释了不同容量和型号颗粒的地址空间分配,并通过1gb ddr颗粒实例说明行地址、列地址和存储单元数据位宽的 .7 of 35 Rev. 1.0 February 2009 Unbuffered SoDIMM DDR3 SDRAM 5.0 Pin Description *The VDD and VDDQ pins are tied common to a single power-plane on these designs. Pin Name Description Number Pin Name Description Number CK0, CK1 Clock Inputs, positive line 2 DQ0-DQ63 Data Input/Output 64This user needs to to pin plan the DDR MC interface, observe PCB layout guidelines and model the physical interface. This user also needs to bring up and debug the DDR MC interface. Related Links. Tutorial: Obtaining and Verifying Versal Adaptive SoC Memory Pinouts. Tutorial: DDR4 and LPDDR4 Timing Models for Hyperlinx DDRx Wizard in .Hun 6, 2022 — Pinout of SDRAM DIMM (168 pin, Unbuffered) and layout of 168 pin DIMM connectorDIMM=Dual Inline Memory Module. Pinouts / Devices / Connectors. card connector pin assignment. SDRAM DIMM (168 pin, Unbuffered) pins and signals. Pinouts > Memory slots and cards connectors. 168 pin SDRAM socket connector. at the .Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3 SDRAM) is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth ("double data rate") interface, and has been in use since 2007.It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random .Hul 14, 2020 — Along with the core changes to density and memory speeds, DDR5 also once again improves on DDR memory’s operating voltages. At-spec DDR5 will operate with a Vdd of 1.1v, down from 1.2v for DDR4.

ddr ram pinout Hardware and Layout Design Considerations for DDR Memory Double Data Rate 4 Synchronous Dynamic Random-Access Memory (DDR4 SDRAM) is a type of synchronous dynamic random-access memory with a high bandwidth ("double data rate") interface.. Released to the market in 2014, [2] [3] [4] it is a variant of dynamic random-access memory (DRAM), some of which have been in use since the early .Centon offers DDR, DDR2, DDR3, DDR4 and DDR5 memory modules for Laptops, Desktops and Servers. DDR Memory Computer Memory SDRAM is synchronous, and therefore relies on a clock to synchronize signals, .Computers built before 2002 generally used synchronous dynamic random-access memory (SDRAM). Fast forward to 2021, and memory technology took a revolutionary stride with DDR5 DRAM. During the years in between, several generations of RAM entered the market. Each generation of RAM increases speed and frequency while decreasing .The PS incorporates an AXI memory port interface, a DDR controller, the associated PHY, and a dedicated I/O bank. DDR3L memory interface speeds up to 533 MHz (1066 MT/s) are supported. Zybo Z7 was routed .Okt 20, 2021 — >>> Register here <<< Ddr2 Ram 8gb; Ddr2 Ram Slot Pinout Adapter; Memory Module Pinouts. 1 is ddr ram and the other is ddr2.ram. Both look very similar and would be hard to tell which is which .The Nexys4 DDR board can receive power from the Digilent USB-JTAG port (J6) or from an external power supply. Jumper JP3 (near the power jack) determines which source is used. All Nexys4 DDR power supplies can be turned on and off by a .The Viking DDR4 UDIMM memory module offers lower operating voltages, higher module densities and faster speed categories than the prior DDR3 generation. JEDEC DDR4 (JESD79-4) has been defined to provide higher performance, with improved reliability and reduced power, thereby representing a significant

In DDR memory, there are 92 single-sided gold finger pins (184 on both sides), 52 pins on the left side of the notch and 40 pins on the right side of the product; DDR2 Memory has 120 gold fingers on one side (240 on both sides), 64 pins on the left side of the notch and 56 pins on the right side of the notch;This annex JESD309-S4-RCE, DDR5 Small Outline Dual Inline Memory Module with 4-bit ECC (EC4SODIMM) Raw Card E Annex" defines the design detail of x8, 2 Package Ranks DDR5 ECC SODIMM. The common feature of DDR5 SODIMM such as the connector pinout can be found in the JESD309, DDR5 Small Outline Dual Inline Memory Module .

ddr ram pinout|Hardware and Layout Design Considerations for DDR Memory

PH0 · SDRAM DIMM (168 pin, Unbuffered) pinout signals

PH1 · Pinout of DDR1, DDR2, DDR3 RAM connectors

PH2 · Hardware and Layout Design Considerations for DDR Memory

PH3 · Desktop DDR4 RAM Pinout

PH4 · DDR3 SDRAM UDIMM

PH5 · DDR3 SDRAM Specification

PH6 · DDR2 SDRAM DIMM 240 pin · AllPinouts

PH7 · DDR SDRAM DIMM 184 Pin · AllPinouts

PH8 · DDR SDRAM DIMM (184 pin, Unbuffered) pinout signals

PH9 · DDR SDRAM